# Kronos: Verifying leak-free reset for a system-on-chip with multiple clock domains

by

### Noah Moroze

B.S., Massachusetts Institute of Technology (2020) Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2021

© Massachusetts Institute of Technology 2021. All rights reserved.

| Author               |                                                          |

|----------------------|----------------------------------------------------------|

| $\mathrm{D}\epsilon$ | epartment of Electrical Engineering and Computer Science |

|                      | January 15, 2021                                         |

| C .:C 11             | ,                                                        |

| Certified by         |                                                          |

|                      | Anish Athalye                                            |

|                      | Doctoral Candidate                                       |

|                      | Thesis Supervisor                                        |

| Certified by         |                                                          |

| cerumed by           | M. Frans Kaashoek                                        |

|                      |                                                          |

|                      | Charles Piper Professor                                  |

|                      | Thesis Supervisor                                        |

| Certified by         |                                                          |

|                      | Nickolai Zeldovich                                       |

|                      | Professor                                                |

|                      | Thesis Supervisor                                        |

| A , 1.1              | •                                                        |

| Accepted by          | 7                                                        |

|                      | Katrina LaCurts                                          |

|                      | Chair, Master of Engineering Thesis Committee            |

# Kronos: Verifying leak-free reset for a system-on-chip with multiple clock domains

by

#### Noah Moroze

Submitted to the Department of Electrical Engineering and Computer Science on January 15, 2021, in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science

#### Abstract

Notary [3] uses formal verification to prove a hardware-level security property called deterministic start for a simple system-on-chip (SoC). Deterministic start requires that an SoC's state is fully reset by boot code to ensure that secrets cannot leak across reset boundaries. However, Notary's approach has several limitations. Its security property requires that all of the SoC's microarchitectural state can be reset to known values through software, and the property and proof technique apply only to SoCs with a single clock domain. These limitations prevent Notary's approach from being applied to more complex systems.

This thesis addresses these limitations through Kronos, a system consisting of a verified SoC that satisfies a new security property called output determinism. Output determinism provides the same security guarantees as Notary without requiring that all of an SoC's state be reset by software. The SoC used in Kronos, called MicroTitan, is based on the open-source OpenTitan [16] and includes multiple clock domains. This thesis evaluates Kronos and demonstrates that existing open-source hardware can be modified to satisfy output determinism with minimal changes, and that the process of proving output determinism reveals hardware issues that violate desired security guarantees.

Thesis Supervisor: Anish Athalye

Title: Doctoral Candidate

Thesis Supervisor: M. Frans Kaashoek

Title: Charles Piper Professor

Thesis Supervisor: Nickolai Zeldovich

Title: Professor

### Acknowledgments

Thank you to Anish Athalye for his invaluable mentorship throughout this project. His research laid the groundwork for this thesis, and his guidance over the course of the project was fundamental to its success. Thank you to Professor Frans Kaashoek and Professor Nickolai Zeldovich, who, along with Anish, frequently provided insightful technical advice, feedback, and support.

Thank you to my friends, who were a source of learning, laughter, and support throughout my time in school. They made the experience truly special, and I look forward to these friendships continuing on beyond graduation. Finally, thank you to my family for their unconditional love and support, and particularly my parents who have always encouraged me to pursue my interests to the fullest extent.

## Contents

| 1 | Intr               | roduction                               | 15 |

|---|--------------------|-----------------------------------------|----|

|   | 1.1                | Background                              | 15 |

|   | 1.2                | Goal and challenges                     | 17 |

|   | 1.3                | Thesis contributions                    | 18 |

|   | 1.4                | Thesis outline                          | 19 |

| 2 | Bac                | ekground                                | 21 |

|   | 2.1                | Deterministic start                     | 21 |

|   | 2.2                | Threat model                            | 23 |

|   | 2.3                | Symbolic execution                      | 23 |

|   | 2.4                | OpenTitan                               | 26 |

|   |                    | 2.4.1 Verification subset               | 27 |

| 3 | Output determinism |                                         |    |

|   | 3.1                | Noninterference without state clearing  | 29 |

|   | 3.2                | Formal reasoning about circuits         | 32 |

|   |                    | 3.2.1 Example circuit                   | 34 |

|   | 3.3                | Formal definition of output determinism | 36 |

| 4 | Mo                 | dular output determinism                | 39 |

|   | 4.1                | Model of multiple clock domains         | 40 |

|   |                    | 4.1.1 Clock domain crossing             | 41 |

|   |                    | 4.1.2 Outputs                           | 41 |

|   | 4.2 | Machine-verified subproperties             | 43         |

|---|-----|--------------------------------------------|------------|

|   |     | 4.2.1 Core output determinism              | 44         |

|   |     | 4.2.2 Peripheral output determinism        | 45         |

|   | 4.3 | Paper proof of top-level claim             | 46         |

|   |     | 4.3.1 Notation                             | 46         |

|   |     | 4.3.2 Proof sketch                         | 46         |

| 5 | Mac | chine verification approach                | <b>4</b> 9 |

|   | 5.1 | Modeling individual clock domains          | 49         |

|   | 5.2 | Core output determinism                    | 51         |

|   | 5.3 | Peripheral output determinism              | 54         |

| 6 | SoC | and toolchain implementation               | 57         |

|   | 6.1 | MicroTitan                                 | 57         |

|   |     | 6.1.1 Modifications for toolchain          | 59         |

|   |     | 6.1.2 Modifications for output determinism | 60         |

|   | 6.2 | Toolchain                                  | 63         |

| 7 | Mac | chine verification implementation          | 65         |

|   | 7.1 | FIFO auxiliary proofs                      | 66         |

|   | 7.2 | Core output determinism                    | 67         |

|   |     | 7.2.1 Boot code                            | 67         |

|   |     | 7.2.2 Performance hints                    | 71         |

|   |     | 7.2.3 Additional output equivalence proof  | 74         |

|   | 7.3 | Peripheral output determinism              | 75         |

|   |     | 7.3.1 SPI-in and SPI-out                   | 76         |

|   |     | 7.3.2 USB                                  | 76         |

| 8 | Eva | luation                                    | <b>7</b> 9 |

|   | 8.1 | Performance                                | 79         |

|   | 8.2 | OpenTitan hardware changes                 | 82         |

|   |     | 8.2.1 Root code                            | 20         |

|                    |      | 8.2.2    | RTL changes                       | 82 |

|--------------------|------|----------|-----------------------------------|----|

|                    | 8.3  | Impact   | t of violating output determinism | 83 |

|                    |      | 8.3.1    | UART RX data leak                 | 84 |

|                    |      | 8.3.2    | SPI TX data leak                  | 84 |

|                    |      | 8.3.3    | SPI RX data leak                  | 85 |

|                    |      | 8.3.4    | Possible USB data leak            | 86 |

| 9                  | Rela | ated W   | $v_{ m ork}$                      | 87 |

|                    | 9.1  | Verifyi  | ng systems software               | 87 |

|                    | 9.2  | Verifyi  | ng hardware                       | 87 |

|                    |      | 9.2.1    | Self-equivalence with don't-cares | 87 |

|                    |      | 9.2.2    | CDC verification                  | 88 |

|                    |      | 9.2.3    | RISC-V formal                     | 89 |

|                    |      | 9.2.4    | Symbiyosys tool                   | 89 |

|                    | 9.3  | Hardw    | are state clearing                | 89 |

| 9.4 Taint tracking |      | tracking | 90                                |    |

|                    | 9.5  | Hardw    | are symbolic execution            | 90 |

| 10                 | Con  | clusion  | 1                                 | 93 |

|                    | 10.1 | Future   | work                              | 93 |

|                    |      | 10.1.1   | Modular reasoning                 | 93 |

|                    |      | 10.1.2   | Scalable verification             | 94 |

|                    |      | 10.1.3   | Persistent storage                | 95 |

|                    |      | 10.1.4   | Design-for-verification           | 95 |

|                    |      | 10 1 5   | Formalizing motathoory            | 06 |

# List of Figures

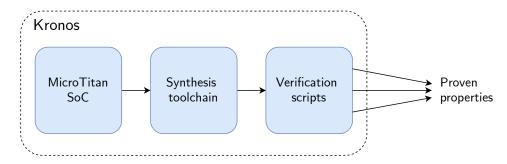

| 1-1 | Overview of Kronos, the system presented by this thesis                   | 19 |

|-----|---------------------------------------------------------------------------|----|

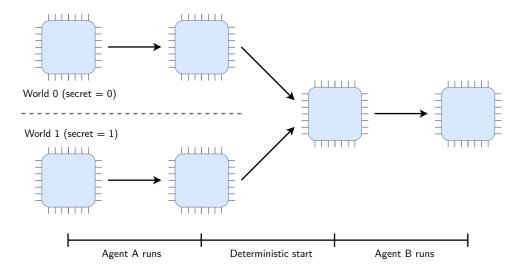

| 2-1 | Deterministic start ensures noninterference between two agents (figure    |    |

|     | adapted from Notary [3])                                                  | 22 |

| 2-2 | Verilog code for symbolic execution example                               | 24 |

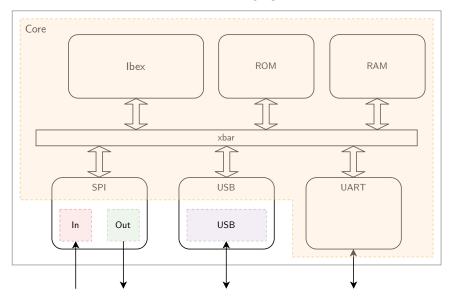

| 2-3 | Block diagram of MicroTitan, Kronos's verified OpenTitan subset.          |    |

|     | Each of the four clock domains is highlighted. Note that each pe-         |    |

|     | ripheral that uses a clock domain other than the core clock domain        |    |

|     | includes hardware in both. In addition, note that the SPI peripheral      |    |

|     | includes two independent clock domains, one for handling input and        |    |

|     | the other for output                                                      | 28 |

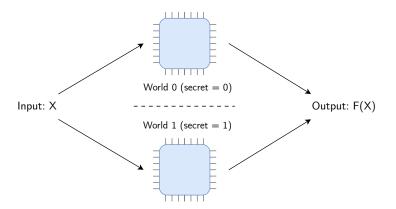

| 3-1 | Circuits may safely contain secrets as long as the circuit functions as a |    |

|     | "black box" where outputs are dependent solely on inputs, not secrets.    |    |

|     | Contrast this with the diagram of deterministic start, Figure 2-1. $$     | 31 |

| 3-2 | Verilog code for circuit with state that is uninitialized on reset, but   |    |

|     | does satisfy ouptut determinism                                           | 32 |

| 3-3 | Example clock domain crossing circuit                                     | 35 |

| 4-1 | MicroTitan split into clock domain subcircuits                            | 40 |

| 4-2 | Diagram illustrating the definition of a CDC register                     | 42 |

| 4-3 | Core output determinism.                                                  | 44 |

| 4-4 | Peripheral output determinism                                             | 45 |

| 5-1 | Example of stepping a circuit in one clock domain while overapproxi-     |    |

|-----|--------------------------------------------------------------------------|----|

|     | mating the other                                                         | 51 |

| 5-2 | Pseudocode for verifying deterministic start with output checking, which |    |

|     | implies output determinism for the core clock domain                     | 53 |

| 5-3 | Pseudocode for verifying output determinism for a peripheral clock       |    |

|     | domain                                                                   | 55 |

| 5-4 | Relation diagram showing output equivalence inductive step. Note         |    |

|     | that in traditional forward simulation, the step functions applied to    |    |

|     | the impl and spec states are different. However, since the impl and      |    |

|     | step states are instances of the same system with no distinction besides |    |

|     | their initial state, they use the same step function                     | 56 |

| 6-1 | Implementation of MicroTitan. Custom components are shaded in or-        |    |

|     | ange with a dotted outline, parts which come directly from OpenTitan     |    |

|     | are shaded in blue with a solid outline                                  | 58 |

| 6-2 | A toolchain for extracting Racket circuit model from SystemVerilog       |    |

|     | source                                                                   | 63 |

| 7-1 | Boot code for MicroTitan                                                 | 68 |

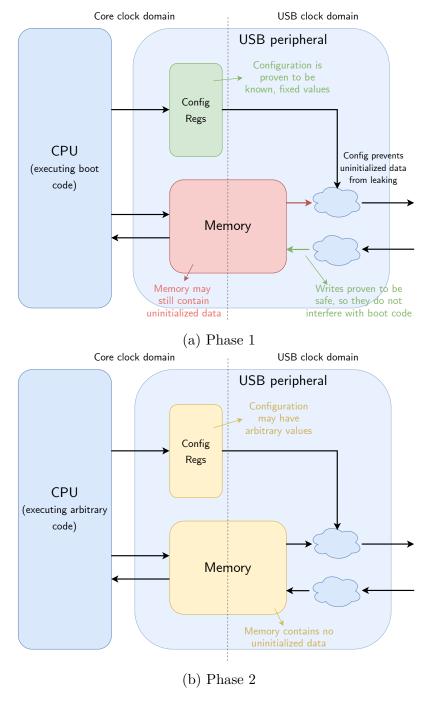

| 7-2 | The two phases of the USB clock domain proof                             | 77 |

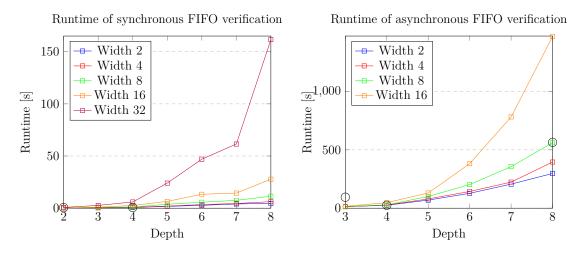

| 8-1 | Graphs of FIFO runtime vs. FIFO size parameters for synchronous          |    |

|     | and asynchronous FIFOs. The black circles represent the parameters       |    |

|     | of FIFOs verified in MicroTitan                                          | 80 |

## List of Tables

| 6.1 | Amount of custom code in MicroTitan                                       | 59 |

|-----|---------------------------------------------------------------------------|----|

| 7.1 | Number of lines of Racket code used to verify each property. These        |    |

|     | counts do not include shared utility code or libraries such as the Racket |    |

|     | DSL for executing SMT-LIB circuits                                        | 65 |

| 7.2 | Which FIFOs are verified by Kronos, including their type (synchronous     |    |

|     | vs asynchronous) and size parameters                                      | 66 |

| 8.1 | Runtime of each verification script                                       | 80 |

| 8.2 | Runtime of verifying output determinism for FIFOs, parameterized by       |    |

|     | type (sync or async), width, and depth                                    | 81 |

| 8.3 | Lines of code required and FPGA resource use for each hardware            |    |

|     | change necessary to ensure MicroTitan satisfies output determinism        | 82 |

### Chapter 1

### Introduction

Formal verification allows researchers and engineers to prove that a system's implementation maintains certain security properties. Formal verification of software typically uses an ideal instruction set architecture (ISA) model, but verifying security properties under an ISA model doesn't rule out vulnerabilities in hardware below the level of the ISA [19]. However, such vulnerabilities do exist. For example, the widely-publicized exploits Spectre [11] and Meltdown [14] are based on vulnerabilities at the microarchitectural level, the low-level implementation of a processor's ISA. Both attacks use side channels in microarchitectural state to leak confidential data. In order to make claims about such attacks, formal verification needs to encompass microarchitectural details too. Towards the goal of extending formal verification to include hardware, this thesis presents Kronos, a system with a hardware-level security property proven using formal verification. This chapter explains the security goals Kronos aims to achieve, the challenges this thesis addresses, a list of this thesis's contributions, and an outline for the rest of the thesis.

### 1.1 Background

This thesis builds off Notary [3], prior work that developed a system with a security property formally verified at the hardware level. Notary is a secure transaction approval device that supports running multiple software "agents" sequentially on the

same SoC (system-on-a-chip, a system that integrates a CPU, memory, I/O, and other peripherals), while guaranteeing *noninterference*, meaning that the execution of one agent on the SoC cannot influence the execution of agents that run subsequently on the same SoC. Noninterference implies that confidential data from one agent cannot leak to another: if an agent operates on secret data, and an agent running later can access that data in some way, this would constitute the first agent influencing the execution of the second.

In order to guarantee noninterference, Notary uses formal verification to prove that the system satisfies a property called *deterministic start*. If a system (which is comprised of an SoC and its boot code) satisfies deterministic start, all of its microarchitectural state is cleared to known, deterministic values by that boot code running after reset. Since microarchitectural state encompasses all channels through which information could leak between agents, ensuring deterministic start before any agent runs also ensures noninterference.

Notary proves deterministic start for a small SoC built around the PicoRV32 [25] RISC-V processor core, a simple, unpipelined processor design with few peripherals and a simple interconnect system for the processor to interface with those peripherals. The PicoRV32 was adequate for running simple agents in the Notary prototype, but using a faster, more complex SoC could enable a Notary-like design to support more demanding applications, such as agents that require a higher performance CPU or more complex peripherals.

An example of an SoC that is a step up from the PicoRV32 in terms of complexity is OpenTitan [16], an open-source SoC being developed for use as a hardware root-of-trust, a security critical application. OpenTitan features a two-stage pipelined processor, yielding higher performance, and a large set of peripherals for I/O and encryption. Proving that this SoC can be used in a system that satisfies noninterference could enable a secure Notary-like architecture to be implemented on a more capable hardware platform, expanding the range of possible applications, while maintaining strong security guarantees.

### 1.2 Goal and challenges

The goal of this thesis is to prove a security property for MicroTitan, a custom subset of OpenTitan hardware, so that it can be used in a Notary-like system that guarantees noninterference. We assume a threat model similar to the one used in Notary, described in more detail in Section 2.2. Although the aim of this thesis is to prove a security property that achieves the same overall security goals as Notary, proving such a property for more complex hardware introduces new challenges that must be addressed.

While Notary relies on resetting all of the PicoRV32's state to guarantee noninterference, OpenTitan's microarchitectural state cannot be fully reset to known values, so an approach based solely on resetting all state will not suffice. Although resetting all microarchitectural state is sufficient to ensure that an SoC can provide noninterference, it is not necessary. For example, a hardware-implemented FIFO queue could store data in memory that is not initialized on reset, and this would be safe as long as the FIFO never outputs uninitialized data (e.g. if it outputs zero when empty). This thesis addresses the challenge of formally defining a security property that is strong enough such that an SoC that satisfies the property can be used in a system that provides noninterference, while not requiring that the SoC's state be entirely resettable.

A second challenge is that Notary's security property and its formal verification approach apply only to circuits with a single clock source, while OpenTitan's SPI and USB peripherals use separate clocks from the main processor. Therefore, the security property and the proof technique used in this thesis must be able to handle circuits with multiple clock domains. It's important to address this challenge since a Notary-like system gives untrusted software direct access to peripherals without going through a kernel, and therefore all peripherals must satisfy the security property required to achieve noninterference.

These are not the only challenges in proving security properties for an SoC like OpenTitan. However, this thesis focuses on addressing these ones in particular, which we believe are associated with common design patterns that would be found in other systems. For instance, it seems likely that other systems may implement I/O with FIFO memories left uninitialized after reset and written by an external source rather than software, requiring a relaxed property that allows for some uninitialized state. Peripherals that implement communication protocols like USB, which by specification requires a 48 MHz clock, most likely require their own separate clock domain.

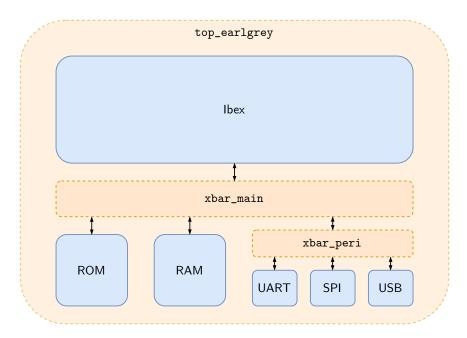

In order to manage the scope of this thesis, Kronos uses a custom subset of the OpenTitan hardware we call MicroTitan. MicroTitan integrates the OpenTitan's Ibex processor with a ROM, RAM, and a subset of OpenTitan communication peripherals which are representative of these challenges: the UART, SPI, and USB peripherals.

#### 1.3 Thesis contributions

This thesis makes several contributions:

- 1. A definition of a security property, *output determinism*, that provides the same security guarantees as Notary's deterministic start but does not require an SoC's state to be fully reset.

- 2. An approach, called *modular output determinism*, for proving output determinism for a digital circuit with multiple clock domains, which consists of:

- (a) A set of properties that are mechanically checked for a particular circuit using formal verification.

- (b) A sketch of a paper proof demonstrating that these mechanically checked properties imply that the circuit satisfies output determinism.

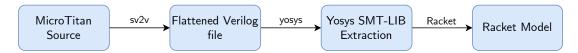

- 3. An implementation of modular output determinism for a subset of the Open-Titan hardware we call MicroTitan. This implementation comprises a system called Kronos, the components of which are illustrated in Figure 1-1. This implementation is open-source, and can be found on Github<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>https://github.com/nmoroze/kronos

Figure 1-1: Overview of Kronos, the system presented by this thesis.

- 4. An evaluation of Kronos, which shows the following:

- (a) The performance of the formal verification implementation demonstrates that modular output determinism is computationally feasible.

- (b) OpenTitan hardware requires changes to satisfy output determinism, but the impact of these changes in terms of circuit size is minimal.

- (c) Proving output determinism catches potential security bugs.

### 1.4 Thesis outline

The rest of this thesis is outlined as follows. Chapter 2 discusses relevant background. Chapter 3 defines the output determinism security property. Chapters 4 and 5 discuss an approach for proving output determinism for a circuit with multiple clock domains. Chapters 6 and 7 describe how Kronos implements this approach for MicroTitan. Chapter 8 evaluates Kronos based on the questions above. Chapter 9 discusses related work. Finally, Chapter 10 concludes and presents ideas for future work.

### Chapter 2

### Background

### 2.1 Deterministic start

Notary's deterministic start resets a hardware system's complete microarchitectural state to known, deterministic values. This enables Notary's goal of allowing two software agents to run sequentially on the same hardware with complete isolation, guaranteeing noninterference.

The key idea behind noninterference, and the reason it is a desirable security property, is that two agents running in a hardware system may be mutually distrusting and have secrets that they want to remain confidential. For example, consider two agents A and B where agent A is meant to sign and approve cryptocurrency transactions with a secret key. A user may execute agent A to sign a transaction, then execute agent B to perform some other task. Agent A will perform the necessary cryptographic signature computations, which will likely leave the secret key in bits of the hardware's state such as RAM, or microarchitectural state such as a cache.

If this state is not cleared before agent B runs, then a malicous agent B might be able extract the secret key and send it to an adversary. This could occur either through obvious channels, such as reading it directly out of memory, or more subtle side channels, such as cache timing data. The possibility of side channels in particular motivates the use of formal verification to ensure that all microarchitectural state is cleared between executions. If all of this state is cleared, there is no way for agent B

Figure 2-1: Deterministic start ensures noninterference between two agents (figure adapted from Notary [3]).

to extract any secrets that may be left over from agent A.

A strawman solution to this problem might be to reset the SoC between executing different agents using the hardware reset line. However, one of Notary's insights is that in real processor designs, simply asserting the hardware reset line does not reset all microarchitectural state. This is because running reset lines to every register is both expensive (in terms of silicon area), and unnecessary for functional correctness. Embedded systems often have boot code that runs after reset that ensures that "architectural state", i.e. state specified by a processor's ISA such as registers and memories, do get overwritten with initial values on reset. However, this does not ensure that microarchitectural state gets cleared.

In order to achieve a high degree of security, Notary extends this idea of initialization boot code through a concept called "software-assisted deterministic start." Software-assisted deterministic start involves writing boot code which is guaranteed to put the processor in a *fully* deterministic state, including architectural and microarchitectural state, when that code is executed after reset.

Proving deterministic start entails both writing this initialization code, and then using formal verification to prove that all microarchitectural state becomes deterministic after the initialization code runs, regardless of the system's starting state.

Although it's not possible to reset all microarchitectural state in a processor such as the OpenTitan, it's clear why this approach prevents secrets from leaking across reset boundaries, and the ideas behind deterministic start inform the approach used for proving output determinism.

#### 2.2 Threat model

Kronos's goal is to prevent an attacker from exfiltrating any secret data that was part of the SoC state prior to the most recent reset. Kronos assumes an attacker can run arbitrary code on the SoC after reset, with full software access to all hardware peripherals. It also assumes the attacker has full access to the SoC's input and output pins, allowing the attacker to snoop on output or send arbitrary inputs to the SoC.

Except for microarchitectural side channels, Kronos's threat model does not include arbitrary side channels [29] such as electromagnetic radiation [2], power analysis [18], and acoustic analysis [10], the same limitations as Notary. Also like Notary, Kronos does not focus on physical attacks.

This threat model is strong enough for MicroTitan to be used in a transaction approval system as implemented in Notary, with the same security guarantees. Considering all I/O untrustworthy captures Notary's assumption that an externally connected device can be compromised or malicious, and allowing the attacker to run arbitrary code with hardware access captures Notary's assumption that software agents with full hardware access may be compromised or malicious.

### 2.3 Symbolic execution

Notary's formal verification technique, which this thesis adopts and extends for proving output determinism, is based on *symbolic execution*. Symbolic execution lets a developer reason about a system's execution efficiently while considering many possible states.

One key concept in symbolic execution is the *symbolic value*, which is a named

```

module example(

2

input clk,

3

input

rst_n,

4

input [7:0] in,

5

6

input

in_valid,

7

output [7:0] out

8

9

10

reg [7:0] data;

11

12

data_valid;

13

14

always @(posedge clk or negedge rst_n) begin

15

if (!rst_n) begin

16

// set data_valid to zero on reset, but don't reset data

data_valid <= 1'b0;</pre>

17

18

end else if (in_valid) begin

data_valid <= 1'b1;

19

20

data <= in;

21

end

22

end

23

24

assign out = data_valid ? data : 8'b0;

26

endmodule

```

Figure 2-2: Verilog code for symbolic execution example.

value that itself represents all possible values of an associated datatype. For example, a symbolic 2-bit value called foo simultaneously represents the values 0, 1, 2, or 3. Symbolic expressions are mathematical expressions based on symbolic values. For example, the symbolic expression foo & 2, which incorporates the previous value foo, could potentially be the value 0 or 2.

Kronos uses the Rosette [23] solver-aided programming library for symbolic execution in the Racket programming language. Rosette lifts many Racket constructs for symbolic execution and supports rich symbolic expressions including bitvectors, vectors of values, arithmetic, conditional operations (ite or "if-then-else"), bitvector concatenation/slicing, and more.

To illustrate how symbolic execution applies to an example circuit, consider the Verilog snippet in Figure 2-2. Suppose this circuit has just been reset, so the values stored in its registers are:

- data\_valid = 1'b0

- data = data\$0

data\$0 is an 8-bit symbolic value, which represents that data is uninitialized on reset, and could contain any possible value from 0 to 255.

Consider what happens when this circuit undergoes a single clock step. To model all possible inputs, we represent the current value of the inputs in and in\_valid with the symbolic values in\$0 and in\_valid\$0 respectively. After the step, the registers have the following values:

- data valid = (ite in valid\$0 1'b1 1'b0) = in valid\$0

- data = (ite in valid\$0 in\$0 data\$0)

Both registers now contain symbolic expressions based on the conditional in the Verilog always block. Note that data\_valid's value can be simplified from a conditional down to just in\_valid\$0. Rosette is able to perform basic simplifications like this using a feature called rewrite rules.

On the other hand, data must remain as a conditional symbolic expression. The meaning of the expression is that if in\_valid\$0 is 1'b1, then data takes on the symbolic value in\$0, otherwise it takes on the symbolic value data\$0.

The value of the output out can now be expressed as the symbolic expression (ite in\_valid\$0 (ite in\_valid\$0 in\$0 data\$0) 8'b0). This symbolic expression contains two nested conditionals, with three leaf values: in\$0, data\$0, and the constant 8'b0. However, close analysis of the expression reveals that it can evaluate to only two possible values: in\$0 or 8'b0. This is because for the second nested conditional to evaluate to data\$0, in\_valid\$0 would have to be equal to 1'b0. However, if in\_valid\$0 is equal to 1'b0, then the whole expression would just evaluate to 8'b0 since the top-level conditional is based off in\_valid\$0 as well. Therefore, data\$0 is not a possible value of this expression.

Although it's easy to determine the possible values of a simple expression like this just by looking at it, the expressions dealt with in real circuits may be much larger and more complex. Therefore, Rosette relies on SMT solvers like Z3 [7] to prove statements about the expressions. In the above example, a developer could use Rosette to verify a statement such as assert out != data\$0. Rosette would call

into an SMT solver, which would analyze the expression to determine that out can never be equal to data\$0.

Notary uses this representation of circuit state as symbolic values and expressions to prove deterministic start. Just like in this example, the state of all registers uninitialized by the hardware reset line are initialized as symbolic values. This models all possible values that may have been left behind in the SoC. After executing boot code using symbolic execution, an SMT solver query proves that no register values may depend on these initial starting symbolic values. By considering all possible starting states in one execution, symbolic execution eliminates the need to exhaustively check each starting state one at a time, which would not be computationally feasible for anything but the simplest circuits.

Symbolic execution is often used for verifying software, but Notary and Kronos apply it to the execution of a cycle-accurate software model of the hardware circuit that implements an SoC.

### 2.4 OpenTitan

The OpenTitan [16] system-on-chip is an open source hardware system that's an appealing target for our work for several reasons:

- It's based on the Ibex [15] processor core, a design that's a step up from Notary's PicoRV32 in complexity with a two-stage pipeline and support for machine and user privilege modes. This enables better performance and the ability to use this core in a system that requires multiple privilege levels, such as allowing agents to take advantage of M/U mode separation or physical memory protection in a Notary-like setting.

- OpenTitan has a large suite of modular peripherals (such as co-processors for encryption and hardware support for multiple communication protocols) that make it more practical to integrate in a larger real-world system.

• OpenTitan is designed for use as a secure silicon root-of-trust in data centers, meaning that its intended use case inherently requires a high degree of security.

OpenTitan's Ibex processor implements the RISC-V ISA, just like the PicoRV32. Using RISC-V allows us to take advantage of its large ecosystem of tools and open-source processor designs.

#### 2.4.1 Verification subset

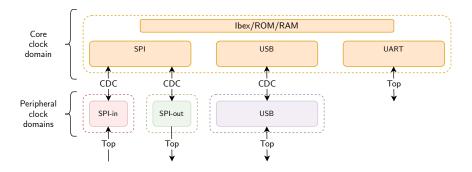

The entire OpenTitan SoC is large—it consists of about 20,000 flip-flops compared to about 1,300 for the PicoRV32 SoC analyzed in Notary. Working with such a large device poses performance challenges for formal verification, and various components of the SoC introduce their own inherent challenges. This thesis focuses on proving properties about a more manageable subset called *MicroTitan*, which consists of about 4,300 flip-flops (around three times the size of PicoRV32, and around one-fifth the size of OpenTitan). Figure 2-3 shows a block diagram of this subset, with the clock domains used in each peripheral highlighted.

MicroTitan includes the Ibex processor, ROM, and RAM, which are the bare minimum required for executing code. Additionally, it includes three I/O peripherals: UART, device-side SPI, and device-side USB. The UART is the simplest of the three, and is clocked by the same clock as the processor. Verifying the UART acts as a simple baseline example of a single clock domain communication peripheral. The SPI and USB peripherals are both implemented in multiple clock domains, and serve as two different examples of how to apply the multiple clock domain verification technique developed by this thesis. OpenTitan is still under active development; this thesis uses the implementation as of commit 97b60c1 in the OpenTitan Git repository.

Since this thesis considers a subset of the OpenTitan's peripherals, we had to implement our own top-level Verilog module to wire them up into one SoC. We carefully constructed our top-level module implementation by copying the relevant sections of OpenTitan's top-level module to make MicroTitan as representative as possible. We use the same crossbar implementation as OpenTitan for connecting the

#### MicroTitan SoC

Figure 2-3: Block diagram of MicroTitan, Kronos's verified OpenTitan subset. Each of the four clock domains is highlighted. Note that each peripheral that uses a clock domain other than the core clock domain includes hardware in both. In addition, note that the SPI peripheral includes two independent clock domains, one for handling input and the other for output.

processor and peripherals.

During the process of verification, we discovered that some of the OpenTitan peripherals used in MicroTitan violate output determinism. In those cases, we implemented minimal patches in order to fix them. These patches are discussed in detail in Section 6.1.2, Section 8.2, and Section 8.3.

### Chapter 3

### Output determinism

This chapter formalizes the property *output determinism*, which can be used to prove a system provides noninterference without requiring an SoC's state be fully cleared. Section 3.1 begins by discussing the intuition behind achieving noninterference without resetting all state, and provides a prose definition of output determinism. Next, Section 3.2 defines concepts and notation that allow us to reason formally about the MicroTitan circuit. Finally, Section 3.3 uses these concepts to formally define output determinism.

### 3.1 Noninterference without state clearing

Notary guarantees noninterference between software agents by proving the deterministic start property. In order for an SoC to satisfy deterministic start, it must be possible to reset the entire state of the SoC to deterministic values by executing code on its processor. However, guaranteeing noninterference solely by clearing state does not work for OpenTitan, which has state that cannot be reset by code.

One example is OpenTitan's SPI input FIFO buffer, which stores data in memory that's not initialized on reset. There is no way of writing to this buffer from software—if an external SPI host does not write to it, then the buffer will contain the same data it did prior to reset. A general security property doesn't assume any particular behavior on the part of an external host, so we can't assume it must write data at

any point. Therefore, we cannot guarantee that the data in this buffer is reset after executing any number of cycles.

However, just because this memory cannot be reset doesn't mean that it can leak uninitialized data. Considering this FIFO example, the hardware could be designed such that when the FIFO is empty, the FIFO data output is hardwired to zero. That way, no hardware modules that use this FIFO will ever be able to extract uninitialized data out of the FIFO memory. If the FIFO ever becomes non-empty, it should have had new data written to its memory that will become visible on the outputs. If the hardware is designed not to leak uninitialized data, it could effectively provide noninterference because a malicious agent will not be able to access any data left behind from a previous execution in a meaningful way.

This example begs the question of what exactly it means for uninitialized data to be "leaked". For example, does it count as leakage if uninitialized data is able to flow from one register to another? This thesis claims that in order to ensure security, the only thing that must not happen is for uninitialized data to influence *observable outputs* of the circuit. If uninitialized data cannot affect outputs, an attacker cannot exfiltrate secrets.

Output determinism is based off this claim: a circuit's state may safely contain secret data as long as externally observable behavior is not dependent on the secret data. If a circuit satisfies this property, it means that a circuit's outputs must be fully determined by its inputs. The definition of output determinism below formalizes this intuition.

**Definition 3.1.1** (Output determinism). If a circuit satisfies output determinism, then the output of the circuit at any step during execution may only depend on the inputs the circuit has received after reset up to that step. The outputs cannot depend on the circuit's state prior to reset.

A circuit that satisfies output determinism provides protection from directly leaking secrets and against timing side-channels, since any observable timing difference as a result of secret data would still mean that output values on any given cycle are

Figure 3-1: Circuits may safely contain secrets as long as the circuit functions as a "black box" where outputs are dependent solely on inputs, not secrets. Contrast this with the diagram of deterministic start, Figure 2-1.

not solely dependent on past inputs. This further means that a circuit that satisfies output determinism can be used in a system that guarantees noninterference, because state left over from the execution of a previous agent cannot influence the execution of subsequent agents in any observable way.

Although output determinism does not require resetting circuit state like deterministic start, it's useful to note that a circuit with its state entirely reset to deterministic values will satisfy output determinism.

This is the case since a circuit's outputs can always be determined by its input and its state. Therefore, the outputs of a circuit with deterministic state can be fully determined solely by its inputs. In addition, a circuit's new state after a clock step can be fully determined by its previous state and its inputs. Therefore, once a circuit has been put into a deterministic state, its state will be fully determined by its inputs from then on, meaning it satisfies output determinism from that point on.

As discussed in the FIFO example above, a circuit's state may not be fully resettable, and yet it may still satisfy output determinism. The Verilog code in Figure 3-2 shows a concrete example of a circuit where this is the case (this is the same code from the symbolic execution example in Section 2.3). The register data is not initialized on reset, and is written only when an external input in\_valid is set to true. Therefore, we can't say for certain that data will be reset to a deterministic state after executing for a known number of cycles. However, this circuit does satisfy output determinism,

```

module example(

2

input clk,

3

input

rst_n,

4

input [7:0] in,

5

6

input

in_valid,

7

8

output [7:0] out

9

10

reg [7:0] data;

11

12

data_valid;

13

14

always @(posedge clk or negedge rst_n) begin

15

if (!rst_n) begin

16

// set data_valid to zero on reset, but don't reset data

data_valid <= 1'b0;</pre>

17

18

end else if (in_valid) begin

19

data_valid <= 1'b1;</pre>

20

data <= in;

21

end

22

end

23

assign out = data_valid ? data : 8'b0;

24

26

endmodule

```

Figure 3-2: Verilog code for circuit with state that is uninitialized on reset, but does satisfy out tut determinism.

since its single top-level output out is fully determined by past inputs on every step. To see that this is the case, consider the two possible values out may have depending on the value of data\_valid. If data\_valid is 1'b1, out will be equal to data. Although data is uninitialized on reset, and thus starts out with an unknown value, its value will be overwritten by the in input at the same time data\_valid becomes 1'b1 (since they both change in the same block). If data\_valid is 1'b0, then out is set to 8'b0, which is a known value. Although data contains uninitialized data while data\_valid is 0, it does not matter since its value never reaches an output.

### 3.2 Formal reasoning about circuits

This section describes a mathematical model for reasoning about the digital circuit that implements the MicroTitan. This model consists of the circuit's state, top-level inputs and outputs, and step function.

MicroTitan is an SoC implemented by a stateful digital circuit comprised of com-

binational logic and registers. This thesis uses the term "register" to refer to all storage elements, including memories. Each register belongs to one or more *clock domains*.

The circuit's state is the set of all values stored in its registers. S is the set of all possible circuit states.

The circuit has some number of input and output wires, referred to as top-level inputs and outputs. I is the set of all possible top-level inputs, and O is the set of all possible top-level outputs.

A step function describes the behavior of the circuit. The step function takes in an initial circuit state, the values of all top-level inputs, a single boolean reset input, and a boolean clock input for each clock domain in the circuit. The function returns the new circuit state reached by stepping the initial state on the given input.

$\hat{C}$  is the set of all possible clock and reset inputs. The step function is written as step:  $S \to I \to \hat{C} \to S$ .  $\hat{C}$  can also be decomposed into the set of all clock inputs C and a separate reset input like so:  $\hat{C} = \{\text{rst=0}, \text{rst=1}\} \times C$ .

The output function out:  $S \to I \to O$  takes in a circuit state, the most recent input, and returns a set of outputs.

A register is "in a clock domain" if that register's value may change when the step function is called with the clock input corresponding to that domain set to true. Note that a register that's updated on the positive edge of a clock signal is in a different clock domain from a register that's updated on the negative edge of the same clock signal, since these two registers are not updated at the same timestep. This overapproximates the behavior of the circuit, since it does not consider the fact that these two clock domains are related. Also note that this model allows the circuit to have registers in multiple clock domains, which supports reasoning about memories with multiple write ports that are clocked in different domains.

The circuit has a single reset input that may reset any register in the circuit (as opposed to one reset per clock domain). Therefore, when the reset input is true, the step function will return a state where each register is set to its circuit-defined reset value if it has one. Any register that does not have a defined reset value will be

stepped as usual based on the clock inputs. This reset is *asynchronous*, meaning that stepping with reset asserted will reset registers in all clock domains regardless of the clock inputs.

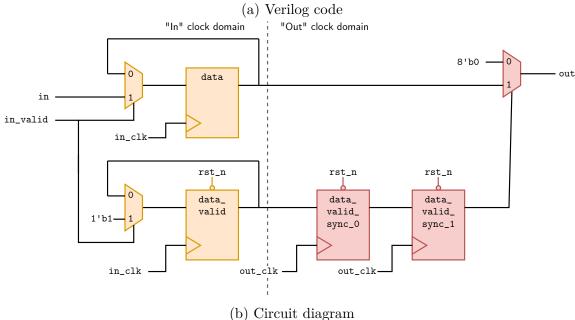

### 3.2.1 Example circuit

To show how this model maps to a concrete example of a simple circuit, Figure 3-3 provides an example circuit in Verilog that extends the circuit provided in Figure 3-2. In this version of the circuit, the data and data\_valid registers are driven by a clock input in\_clk, while out is intended to be read from a separate clock domain driven by out\_clk. Therefore, the data\_valid signal is synchronized through two registers in the output clock domain, data\_valid\_sync\_0 and data\_valid\_sync\_1.

The model categorizes each component of this circuit:

- The circuit's state consists of the values of each of its registers: data, data\_valid, data\_valid\_sync\_0, and data\_valid\_sync\_1.

- in\_clk and out\_clk correspond to the "in" and "out" clock domain inputs, respectively. rst\_n is the global asynchronous reset.

- The top-level inputs to this circuit are in and in\_valid.

- The sole top-level output of this circuit is out.

- data and data\_valid are in the "in" clock domain, since their values are only updated on the positive edge of in clk.

- data valid sync 0 and data valid sync 1 are in the "out" clock domain.

```

1

module example_multiclk(

2

in_clk,

input

3

input

out_clk,

4

input

rst_n,

5

6

input [7:0]

in,

7

input

in_valid,

8

9

output [7:0] out

10

);

11

reg [7:0] data;

data_valid;

12

reg

13

reg

data_valid_sync_0;

14

data_valid_sync_1;

15

always @(posedge in_clk or negedge rst_n) begin

16

17

if (!rst_n) begin

18

// set data_valid to zero on reset, but don't reset data

data_valid <= 1'b0;</pre>

19

20

end else if (in_valid) begin

data_valid <= 1'b1;

21

data <= in;

22

23

end

24

end

25

26

always @(posedge out_clk or negedge rst_n) begin

27

if (!rst_n) begin

28

data_valid_sync_0 <= 1'b0;</pre>

29

data_valid_sync_1 <= 1', b0;</pre>

30

end else begin

31

data_valid_sync_0 <= data_valid;</pre>

32

data_valid_sync_1 <= data_valid_sync_0;</pre>

33

end

34

35

36

assign out = data_valid_sync_1 ? data : 8'b0;

37

38

endmodule

```

Figure 3-3: Example clock domain crossing circuit.

### 3.3 Formal definition of output determinism

We want to prove that MicroTitan satisfies output determinism. Output determinism means that for any given sequence of inputs, the SoC output trace after executing an arbitrary number of cycles should be a deterministic function of its input trace after reset. Definition 3.3.1 below is a formal definition of this property.

First, we define the helper function  $\operatorname{run}: \forall n, S \to I^n \to C^n \to S$  which describes n cycles of execution with a sequence of inputs while reset is not held:

$$\begin{split} &\operatorname{run}\!\left(s,\,[],\,\,[]\right) &= s \\ &\operatorname{run}\!\left(s,\,i::\vec{\imath},\,\,c::\vec{c}\right) &= \operatorname{run}\left(\operatorname{step}(s,i,(c,\operatorname{rst=0})),\vec{\imath},\vec{c}\right) \end{split}$$

This function is then used to formally define output determinism as follows:

**Definition 3.3.1** (Output determinism).

$$\forall i_0 \in I, c_0 \in C, \exists \Omega \in O, \forall s, s_0 \in S,$$

(Base case)

$s_0 = \text{step}(s, i_0, (c_0, \text{rst}=1)) \implies \text{out}(s_0, i_0) = \Omega$

$$\forall n \in \mathbb{N}, \vec{i} \in I^n, \ \vec{c} \in C^n, \exists \Omega \in O, \forall s, s_0, s_n \in S,$$

$$s_0 = \text{step}(s, \vec{i} \ [0], (\vec{c} \ [0], \text{rst} = 1)) \implies$$

$$s_n = \text{run}(s_0, \vec{i} \ [1 :], \vec{c} \ [1 :]) \implies$$

$$\text{out}(s_n, \vec{i} \ [-1]) = \Omega$$

(Inductive step)

This property is expressed recursively. The base case shows that on the initial step where the hardware reset line is asserted, the circuit outputs must be equal to a value  $\Omega$  that only depends on the circuit's input and clock signals on that step,  $i_0$  and  $c_0$ . Importantly,  $\Omega$  must not depend on the circuit's starting state s, which is denoted by the order of the quantifiers.

The recursive step shows that after executing the circuit for n cycles starting from its post-reset state  $s_0$ , its most recent output  $\operatorname{out}(s_n, i)$  must be equal to a value  $\Omega$  that only depends on the input and clock signal trace for the past n cycles. Just like in the base case, the order of the quantifiers indicates that  $\Omega$  may only be dependent on these inputs, and may not depend on the starting state s. Since this property holds for all n, and  $\Omega$  may depend on n as well, this step illustrates that our output on every cycle after reset must be determined by the past input and clock signal trace.

# Chapter 4

# Modular output determinism

This chapter describes an approach for proving output determinism for a circuit with multiple clock domains. One challenge in coming up with such an approach is that the clocks do not step in a fixed, constant ratio (such as "clock domain A steps 2 times for every 1 step of clock domain B"). The OpenTitan SPI peripheral contains logic driven by a clock that can be started and stopped arbitrarily by an external host (i.e., it is not constant), and it is not required to run at a particular frequency (i.e., the ratio is not fixed). This makes it impossible to reason precisely about an execution of the entire circuit as a whole, since there are effectively infinite possible traces of clock inputs.

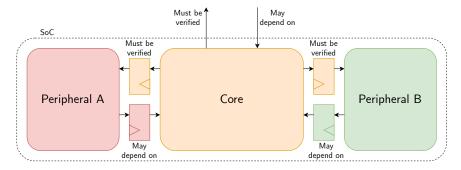

The approach described in this chapter, called modular output determinism, addresses this challenge by dividing up MicroTitan's circuit into multiple logical "subcircuits" comprising of the registers in each clock domain, and then using formal verification to prove properties about each individual subcircuit separately. A proof sketch shows that the properties proven about each subcircuit together imply a top-level property about MicroTitan as a whole.

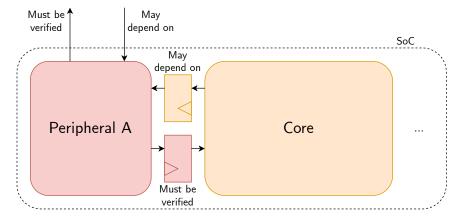

Figure 4-1 shows MicroTitan broken up into separate subcircuits for each clock domain. Note that each subcircuit has its own top-level inputs and/or outputs that communicate externally, labelled "top" in the figure. However, in addition, we can consider the inputs and outputs of each subcircuit to also include the signals that communicate between clock domains, which are labelled "CDC" (clock domain cross-

Figure 4-1: MicroTitan split into clock domain subcircuits.

ing) in the figure. The key idea behind modular output determinism is to prove that each subcircuit in MicroTitan satisfies an output determinism-like property, considering both CDC and top-level inputs and outputs. That is, for each cycle after reset, each clock domain's CDC and top-level outputs must be fully determined by its CDC and top-level inputs.

The intuition behind this technique is that if no secrets leak across clock domain crossing boundaries, then it's okay for top-level outputs to depend on data that's in clock domain crossing boundaries. Therefore, each subcircuit needs to have the data that flows between clock domain crossing boundaries verified along with the data that flows in and out of the circuit as a whole.

In order to express this idea more precisely, Section 4.1 defines concepts necessary to discuss the input and output boundaries of clock domain subcircuits. Section 4.2 defines the machine-verified modular output determinism subproperties that must be proven for each clock domain, and Section 4.3 provides a sketch of a proof that these subproperties imply top-level output determinism.

# 4.1 Model of multiple clock domains

Modular output determinism takes advantage of the fact that MicroTitan's circuit has a particular clock domain topology in order to categorize each clock domain in one of two categories. A single *core* clock domain communicates with three *peripheral* clock domains, with the key restriction that the peripheral clock domains cannot

communicate with each other. The core clock domain is the SoC's primary clock domain, which includes the Ibex CPU, ROM, RAM, UART, and communication hardware between all peripherals. The peripheral clock domains are part of the SPI and USB peripherals. Figure 4-1 points out the two categories of clock domains.

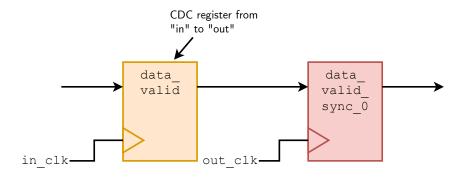

## 4.1.1 Clock domain crossing

The concept of "clock domain crossing" (CDC) registers formalizes the input/output boundaries between clock domains.

**Definition** (CDC register). Suppose we have a circuit with clock domains A and B. A CDC register from A to B is a register that:

- is in clock domain A but not in clock domain B.

- has an output that drives a register in clock domain B (directly or through combinational logic with other registers in any clock domain).

Note that this definition does not consider registers in multiple clock domains to be CDC registers. These cases use special logic that isn't captured by general reasoning about CDC registers. In the case of MicroTitan, the one instance of this is the dual-port memory in the USB peripheral. Section 7.2.1 and Section 7.3.2 discuss how this is handled in the implementation.

Also note that a register can drive registers in multiple clock domains and still be considered a CDC register. For example, a register in clock domain A that drives a register in clock domain A and clock domain B is still considered a CDC register from A to B.

To see how this definition applies to a concrete example, Figure 4-2 shows a snippet of the circuit diagram for Figure 3-3. In this circuit, data\_valid is a CDC register from the "in" to "out" clock domains.

# 4.1.2 Outputs

Modular output determinism requires associating each top-level output with a par-

Figure 4-2: Diagram illustrating the definition of a CDC register.

ticular subcircuit. The most straightforward way to do this would be to associate a top-level output with a certain clock domain if that output is entirely derived from registers in that clock domain. For the most part, this is how MicroTitan's top-level outputs are categorized by Kronos.

However, this straightforward categorization does not always apply. Consider the circuit in Figure 3-3. The output out is combinationally dependent on registers in two different clock domains. This scenario also comes up in MicroTitan. The miso\_o output from the SPI peripheral directly depends on registers from the SPI-out and core clock domains.

In order to handle these cases, modular output determinism does not consider the categorization of top-level outputs as inherently defined by the circuit. Rather, it is left to be chosen by a proof developer as a matter of proof strategy. In fact, subcircuit top-level outputs don't even have to correspond with the circuit's top-level outputs. Modular output determinism's only requirement is that the top-level outputs of each subcircuit (together with the circuit's top-level inputs) fully determine the top-level outputs of the circuit itself.

Suppose  $\operatorname{out}_{CD}$  represents the top-level outputs from each subcircuit CD for  $CD \in \{\operatorname{core}, \operatorname{spi-in}, \operatorname{spi-out}, \operatorname{usb}\}$ , given the current circuit state and inputs. Another way to describe this requirement is it must be possible to determine an output combination function  $\omega$  such that for any given state s and set of inputs i:

$$\mathtt{out}(s,i) = \omega(\mathtt{out}_{\mathtt{core}}(s,i),\mathtt{out}_{\mathtt{spi-in}}(s,i),\mathtt{out}_{\mathtt{spi-out}}(s,i),\mathtt{out}_{\mathtt{usb}}(s,i),i)$$

$\omega$  may rely directly on i since top-level outputs may be driven by combinational logic of the top-level inputs directly.

The distinction between each set of outputs relates solely to the verification approach. Modular output determinism requires the outputs from each clock domain subcircuit only depend on the CDC and top-level inputs to that clock domain. As long as it is possible to verify this, and an  $\omega$  function can be found, then a given categorization of outputs is okay. If these requirements cannot be met, a new categorization of outputs must be chosen. If no output categorization meets these requirements, then modular output determinism cannot be applied to the circuit.

In Figure 3-3, since the output out is driven by two registers each in a different clock domain, data\_valid\_sync\_1 and data, each of those registers could be considered a top-level output of their respective clock domain (even though they don't correspond to circuit top-level outputs themselves). Then the value of out could be captured by the function  $\omega$  like so (assuming  $\Omega$  represents outputs from the "in" clock domain, and  $\Theta$  represents outputs from the "out" clock domain):

$$\omega(\Omega, \Theta, i) = \begin{cases} 0, & \text{if } \Theta_{\texttt{data\_valid\_sync\_1}} = 0 \\ \Omega_{\texttt{data}}, & \text{otherwise} \end{cases}$$

The output categorization is the only concept described in this section that is decided by the developer. The clock domain subcircuits, the categorization of clock domains as *core* or *peripheral*, and which registers are CDC registers are inherently described by the circuit.

# 4.2 Machine-verified subproperties

In order to prove top-level output determinism, modular output determinism requires proving a subproperty called *core output determinism* for the circuit's core clock domain, and a subproperty called *peripheral output determinism* for each peripheral clock domain. These subproperties are similar to output determinism, but with the

Figure 4-3: Core output determinism.

key difference that they include CDC registers as part of the input and output boundaries. This section defines these two subproperties.

# 4.2.1 Core output determinism

The first property is called core output determinism. It is defined as follows.

**Definition 4.2.1** (Core output determinism). If a circuit satisfies core output determinism, then on every step the top-level outputs of the core clock domain subcircuit and the CDC register values from the core clock domain to every peripheral clock domain may depend only on the circuit's top-level inputs and CDC register values from any peripheral clock domain. However, immediately after the step on which reset is asserted, the top-level outputs and CDC registers from the core clock domain may depend on top-level inputs *only*, not CDC register values.

Figure 4-3 provides an example of what proving core output determinism entails. All outputs of the core clock domain subcircuit, including top-level outputs and CDC register values flowing out of the subcircuit, must be verified, and are allowed to depend on top-level inputs and CDC register values flowing into the subcircuit. However, just like regular output determinism the outputs may not depend on uninitialized data left over in the core clock domain.

Note that Definition 4.2.1 specifies that outputs may not depend on CDC register values on reset—this is important for the soundness of modular output determinism.

Figure 4-4: Peripheral output determinism.

# 4.2.2 Peripheral output determinism

The second property is peripheral output determinism. This property is similar to core output determinism. The main distinction is that this property refers to *individual* peripheral clock domains which communicate with the core clock domain, whereas core output determinism refers to CDC communication between the core and *all* peripheral clock domains.

**Definition 4.2.2** (Peripheral output determinism for P). If a circuit satisfies peripheral output determinism for some clock domain P, then on every step the top-level outputs of P's subcircuit and the CDC register values from P to the core clock domain may depend only on the circuit's top-level inputs and CDC register values from the core clock domain to P. However, immediately after the step on which reset is asserted, the top-level outputs and CDC registers from P may depend on top-level inputs only, not CDC register values.

Modular output determinism requires that peripheral output determinism be proven individually for each peripheral clock domain, hence the definition of the property being parameterized by P.

Figure 4-4 illustrates what proving peripheral output determinism entails. All outputs of the peripheral clock domain subcircuit, including top-level outputs and CDC register values must be verified, and are allowed to depend on top-level inputs and CDC register values flowing into the subcircuit. However, just like regular output

determinism the outputs may not depend on uninitialized data left over in the core clock domain. Since peripheral output determinism only deals with one particular peripheral clock domain at a time, only one peripheral clock domain is depicted here.

# 4.3 Paper proof of top-level claim

Modular output determinism claims that proving core output determinism and proving peripheral output determinism for each peripheral clock domain implies output determinism for the entire circuit. This section presents a high-level argument for why this claim is true.

## 4.3.1 Notation

This subsection introduces additional notation to succinctly describe several concepts.  $[C \underset{CDC}{\rightarrow} P]_n$  represents the values of CDC registers from the core clock domain to some peripheral clock domain P on cycle n. Analogously,  $[P \underset{CDC}{\rightarrow} C]_n$  represents the values of CDC registers from some peripheral clock domain P to the core clock domain on cycle n.  $[C \underset{CDC}{\rightarrow} P*]_n$  represents the values of CDC registers from the core clock domain to all peripheral clock domains on cycle n. Analogously,  $[P*\underset{CDC}{\rightarrow} C]_n$  represents the values of CDC registers from all peripheral clock domains to the core clock domain on cycle n.

All of the above values are indexed assuming n = 0 represents the register values corresponding to the state immediately *after* the circuit is stepped with reset asserted.

Let  $i_n$  repesent the circuit's top level inputs on cycle n. In this case, treat the index such that n = 0 is the input to the circuit when it is stepped with reset asserted.

## 4.3.2 Proof sketch

One subtle point that makes it difficult to see why the two subproperties imply output determinism is that it may seem like there's a circular dependency between properties 4.2.1 and 4.2.2. Core output determinism assumes that CDC registers

from peripheral clock domains are "safe" and allows CDC registers from the core clock domain to depend on them, while peripheral output determinism assumes that CDC registers from the core clock domains are "safe" and allows CDC registers from the peripheral clock domains to depend on them.

However, there is no circular dependency issue. On the very first cycle when the circuit is reset, the resulting CDC register values are not allowed to depend on any previous CDC register values, only top-level inputs. At any given cycle after that, the allowed CDC register dependencies from other clock domains are the values from the *previous* step, which have already been proven safe. This intuition is captured in the proof of this following lemma, which is ultimately used to prove that the two modular output determinism subproperties prove output determinism.

**Lemma 1.** If a circuit satisfies property 4.2.1, and satisfies property 4.2.2 for all of its peripheral clock domains, then all of the circuit's CDC register values at every cycle n only depend on the top-level inputs the circuit receives between reset and cycle n, i.e.  $i_0 \dots i_n$ .

*Proof.* We prove this lemma by strong induction.

**Base case.** First, consider the cycle when the circuit is reset (cycle 0). By the definition of property 4.2.1 we can see that  $[C \xrightarrow{CDC} P^*]_0$  only depends on  $i_0$ . By the definition of property 4.2.2, we can see that for every peripheral clock domain P,  $[P \xrightarrow{CDC} C]_0$  only depends on  $i_0$ . Therefore, all CDC register values can be fully determined by the top-level inputs on cycle 0.

**Inductive step.** Assume lemma 1 holds on every cycle k such that  $0 \le k < n$ . We must show that lemma 1 holds for cycle n.

By property 4.2.1 we know that  $[C \underset{CDC}{\rightarrow} P^*]_n$  only depends on  $i_0 \dots i_n$  and  $[P^* \underset{CDC}{\rightarrow} C]_0 \dots [P^* \underset{CDC}{\rightarrow} C]_{n-1}$ . However, since we assume lemma 1 holds for all k < n, we know that  $[P^* \underset{CDC}{\rightarrow} C]_0 \dots [P^* \underset{CDC}{\rightarrow} C]_{n-1}$  must only depend on top level inputs. Therefore,  $[C \underset{CDC}{\rightarrow} P^*]_n$  itself only depends on top-level inputs.

By property 4.2.2 we know that for each peripheral clock domain P,  $[P \xrightarrow[CDC]{} C]_n$  only depends on  $i_0 \dots i_n$  and  $[C \xrightarrow[CDC]{} P]_0 \dots [C \xrightarrow[CDC]{} P]_{n-1}$ . We can use a symmetrical argument to the one above: since we assume lemma 1 holds for all k < n, we know that for every peripheral clock domain P that  $[P \xrightarrow[CDC]{} C]_0 \dots [P \xrightarrow[CDC]{} C]_{n-1}$  must only depend on top-level inputs, and therefore  $[P \xrightarrow[CDC]{} C]_n$  only depends on top-level inputs.

Since both  $[C \xrightarrow{CDC} P*]_n$  and  $[P \xrightarrow{CDC} C]_n$  for every P only depend on top-level inputs, all CDC register values only depend on top-level inputs for cycle n, and lemma 1 holds.

Now, we use the result in lemma 1 to prove the following theorem.

**Theorem 1.** If a circuit satisfies property 4.2.1, and satisfies property 4.2.2 for all of its peripheral clock domains, then that circuit satisfies output determinism as specified in definition 3.1.1.

*Proof.* By property 4.2.1, we know that the top-level outputs of the core clock domain subcircuit may only depend on top-level inputs and CDC register values. By lemma 1, we know that CDC register values themselves may only depend on top-level inputs. Therefore, the top-level outputs of the core clock domain may only depend on top-level inputs.

Applying the same logic as above, property 4.2.2 and lemma 1 also show the top-level outputs of every peripheral clock domain only depend on top-level inputs.

Therefore, the top-level outputs of every subcircuit in our circuit only depend on top-level inputs.

A final observation is that the top-level outputs of a circuit can be determined by the top-level outputs of each subcircuit, as well as the top-level inputs to a circuit. This is true by definition, since as discussed in Section 4.1.2 it must be possible to find a function  $\omega$  such that this is the case. This means that since the top-level outputs of each subcircuit only depend on top-level inputs, the top-level outputs of the circuit itself also only depend on top-level inputs. Therefore, the circuit itself must satisfy output determinism.

# Chapter 5

# Machine verification approach

This chapter describes Kronos's approach for verifying property 4.2.1 and verifying property 4.2.2 for every peripheral clock domain in MicroTitan. Section 5.1 discusses a high-level method for reasoning about individual clock domains in the presence of other clock domains, and Section 5.2 and Section 5.3 go into detail about how core output determinism and peripheral output determinism are verified, respectively.

# 5.1 Modeling individual clock domains

Modular output determinism requires proving properties about individual clock domains. However, since clock domains interact through clock domain crossing, this requires a way to correctly model the execution of a particular clock domain in the presence of others.

Imagine reasoning about a particular clock domain, referred to as the "reference" clock. One way to reason about arbitrary clock signals is to consider that for every step of the reference clock, other clocks may step zero or more times. This captures all possible behaviors of the circuit with respect to its clock inputs, since it allows for any ratio of clock frequencies (including for either clock not to step at all), and it does not require the ratio of clock steps to be fixed throughout the circuit's execution.

Stepping a single reference clock domain on a given set of inputs can be thought of as calling the circuit step function with those same inputs but with only the corresponding clock input set to true. For example, a step function for the core clock domain,  $\mathtt{step}_C \colon S \to I \to \{0,1\} \to S$  can be expressed as:

$$\mathtt{step}_C(s,i,r) = \mathtt{step}(s,i,\{\mathsf{core} = 1,\mathsf{spi\text{-}in} = 0,\mathsf{spi\text{-}out} = 0,\mathsf{usb} = 0,\mathsf{rst} = \mathsf{r}\})$$

Symbolic execution can't directly model an unbounded number of clock steps in between steps of our reference clock. However, it can *overapproximate* the set of possible states after performing one reference clock step. Overapproximation entails setting all registers in non-reference clock domains to completely unconstrained symbolic values. This captures the full set of possible behaviors since other clock steps may only modify the state in non-reference clock domains, and overapproximating makes no attempt at constraining how these values are modified.

Therefore, the behavior of a single reference clock domain in the presence of multiple clock domains can be modelled by calling the corresponding step function, overapproximating the result, stepping the result of the overapproximation, overapproximating the new result, and so on for any number of steps.

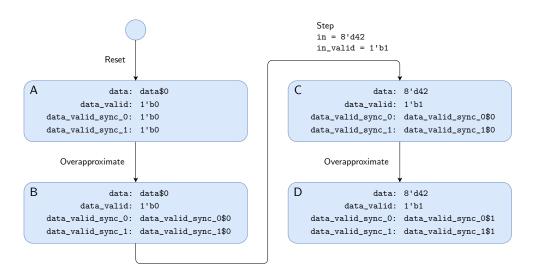

Figure 5-1 provides an example of how the state of the circuit in Figure 3-3 changes when stepped from the perspective of the "in" clock domain. It begins with reset, after which all initialized registers have concrete values, and the uninitialized register data has some symbolic value (Figure 5-1 box A).

After reset, out\_clk may step zero or more cycles before in\_clk steps even once, since it may be arbitrarily faster or slower than in\_clk. Therefore, the state of both data\_valid\_sync\_\* registers are unknown before in\_clk steps. By analyzing the circuit, we can see that their value cannot be anything other than 1'b0. However, this would not always be clear—for example, consider what would happen if this clock domain had a cycle counter register. This register could contain any possible value. Therefore, instead of trying to consider exactly what possible states could be in other clock domains, they are overapproximated entirely by setting the registers to fresh symbolic values (Figure 5-1 box B).

Figure 5-1 box C then shows the outcome of stepping the circuit with a pair of

Figure 5-1: Example of stepping a circuit in one clock domain while overapproximating the other.

concrete inputs, in\_valid = 1'b1, and in = 8'd42. Despite the "in" clock domain now being full of concrete values, we still can't say anything about the possible values of the "out" clock domain, which may once again step for zero or more cycles. So, it must be overapproximated again with fresh values, giving the final state shown in Figure 5-1 box D.

By overapproximating in this manner, we end up considering a superset of possible circuit states (hence the term "overapproximation"). However, this is fine for the soundness of a proof: if a property holds for a superset of the possible circuit states, then it must also hold for the subset of states that are actually possible.

# 5.2 Core output determinism

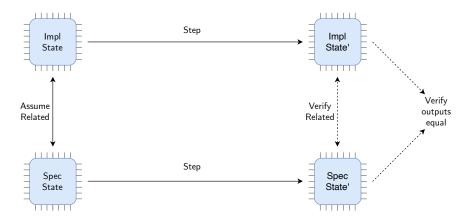

To prove core output determinism, Kronos takes advantage of the fact that it's possible to reason about code executing in the core clock domain, since it includes the actual processor component of the SoC. This allows Kronos to use a "software-assisted" approach similar to Notary, where it reasons about boot code execting on the processor after reset.

One key insight is that if a circuit ends up in a deterministic state, its outputs will be determined solely by its inputs from that point on. A circuit's new state after a step is determined solely by its previous state and input. Therefore, after a circuit reaches a deterministic state, all future states that circuit reaches can be determined solely by its inputs. In addition, a circuit's output on a given cycle is determined by its state and input on that cycle. Putting this together, the circuit's outputs can be solely determined by its inputs on every cycle after the circuit reaches a deterministic state.

Kronos borrows Notary's software-assisted deterministic start approach to use boot code to put MicroTitan's core clock domain in a state where all registers only depend on past inputs and conclude that its output will only depend on its inputs for all future cycles. However, this is insufficient to fully imply core output determinism, since the property requires that a circuit's outputs be safe for all cycles after the reset line is deasserted (including the cycles during which boot code executes). To account for this, Kronos adds "output checking" to deterministic start, which entails verifying that the output on every cycle of boot code execution depends only on past input. This is a straightforward addition since deterministic start is implemented by symbolically executing boot code on the SoC, allowing Kronos to reason about all possible outputs during boot code execution.

With this extra output checking, deterministic start shows that outputs only depend on inputs on every cycle during boot code execution, and implies this is the case for every cycle after boot code execution, which together implies this property for all cycles. Therefore, deterministic start with output checking is sufficient to imply core output determinism.